突破带宽极限!三星 VLSI 2025 展示 212.5Gb/s 超高速接收机设计

背景与核心规格

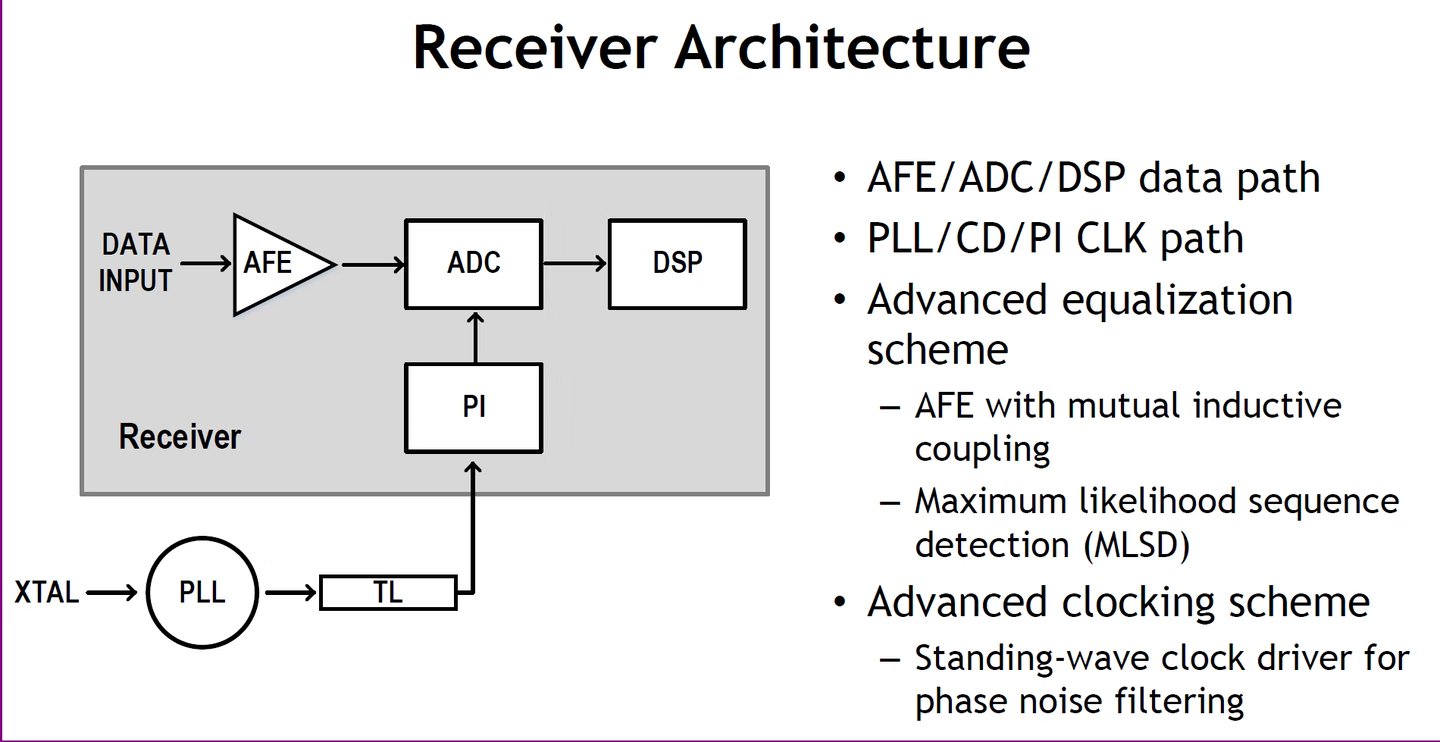

在 VLSI 2025 国际会议上,三星电子(Samsung Electronics)发布了一款基于 4nm FinFET 工艺的 212.5Gb/s PAM-4 DSP 接收机(RX)。这款设计不仅展示了超高的传输速率,更具备应对 40dB 链路插入损耗的强悍性能。🚀

创新点:突破带宽瓶颈的互感 Gm-TIA

在超高速 SerDes 的模拟前端(AFE)设计中,寄生电容与大带宽的矛盾一直是工程师的痛点。传统的解决方案如减小负载电阻或使用分流峰值(Shunt Peaking)往往效果有限。三星的研究团队提出了一种极具创意的思路:利用输入和输出电感之间的强耦合形成正反馈。 ⚡

- 设计思路: 并非采用传统的 T-Coil,而是利用输入侧电感(L1)与输出侧电感(L2)之间的互感(M)来加速信号翻转。

- 性能飞跃: 这种机制在模拟中表现优异。无电感辅助时带宽仅为 25.7GHz,普通分流峰值可提升至 33.9GHz,而引入这种互感正反馈后,带宽大幅跃升至 61.7GHz。

架构优化与稳定性保障

除了核心的 TIA 设计,团队还针对电路的整体稳定性与信号质量进行了多项优化:

- 稳定性增强: 为了维持推挽式 CTLE 的输出共模稳定性,设计中引入了稳定性增强缓冲器(Stability-Enhancing Buffer),将 CMFB 环路的次极点推向更高频,确保相位裕度达到 73°。🛡️

- 驻波时钟驱动器: 放弃了功耗较高的传统 CML 缓冲链,转而采用基于传输线的驻波驱动器(Standing-Wave Driver)。该谐振结构充当了天然的带通滤波器,成功将积分抖动从 57.8fs rms 降低至 55.4fs rms。

实测表现与结论

在实测阶段,该芯片在经过 40dB 损耗的信道后,配合 FFE/DFE 和 MLSD(最大似然序列检测)算法,在 212.5 Gb/s 下实现了低于 6e-6 的误码率。整颗芯片的总功耗为 675.2mW,展示了 4nm 工艺下超高速接口设计的顶尖水准。📊

1

0

用户277037768

关注

75

粉丝

374

获赞与收藏

240

返利网客户端

返利网客户端

评论(0)

查看更多评论